实验教学资源 > 典型实验项目案例

典型实验项目案例

(一)热氧化工艺鸟嘴效应仿真实验案例

A. 实验目的和意义

为了使学生能够更深入、更直观地理解硅的热氧化工艺及鸟嘴效应的原理,掌握不同热氧化条件对氧化层制备和鸟嘴形貌的影响,获得鸟嘴形貌与工艺参数之间的内在联系,采用Silvaco器件与工艺TCAD仿真工具进行热氧化工艺鸟嘴效应模拟实验。

B. 实验步骤

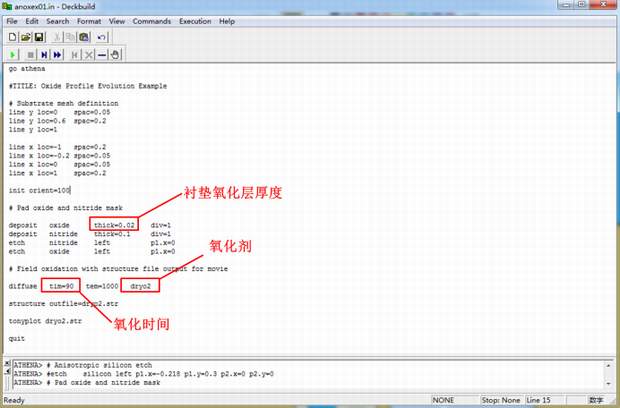

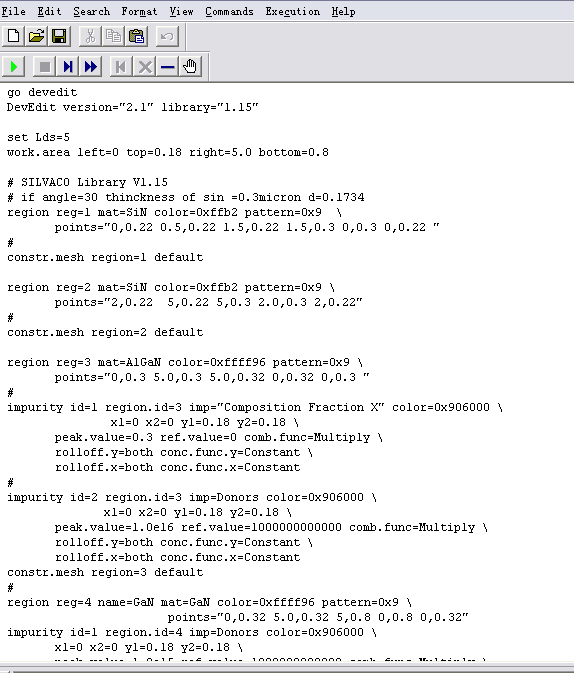

1.打开Silvaco软件中的deckbulid程序运行窗口,并调入基本模拟程序。图1为Silvaco软件中deckbulid程序运行窗口以及基本模拟程序,图中标注出了模拟中所关注的氧化时间、衬垫氧化层厚度和氧化剂三个参数。

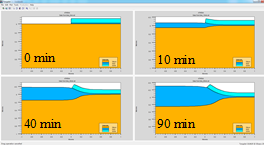

2.改变氧化时间工艺模拟:设置氧化剂为湿氧,氧化温度为1000℃,掩蔽氮化硅薄膜厚度0.1μm,衬垫氧化层厚度为0.02μm,设置氧化时间分别为0min、10min、40min和90min,运行程序,并利用Tonyplot模块输出不同氧化时间时的鸟嘴形貌,分析鸟嘴形貌的分布特点和规律。

图1 Silvaco软件中deckbulid程序运行窗口及基本模拟程序

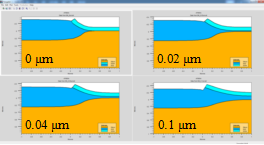

3.改变衬垫氧化层厚度工艺模拟:设置氧化剂为湿氧,氧化时间为90min,氧化温度为1000℃,掩蔽氮化硅薄膜厚度0.1μm,设置衬垫氧化层厚度分别为0μm、0.02μm、0.04μm和0.1μm,运行程序,并利用Tonyplot模块输出不同衬垫氧化层厚度时的鸟嘴形貌,分析鸟嘴形貌的分布特点和规律。

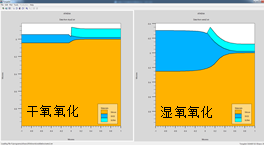

4.改变氧化剂工艺模拟:设置氧化时间为90min,氧化温度为1000℃,衬垫氧化层厚度为0.02μm,掩蔽氮化硅薄膜厚度0.1μm,设置氧化剂分别为干氧、湿氧,运行程序,并利用Tonyplot模块输出不同氧化剂时的鸟嘴形貌,分析鸟嘴形貌的分布特点和规律。

C. 实验结果分析

图2为不同氧化时间时鸟嘴形貌。由图可见,氧化时间为零,即未氧化时,硅片表面平整。氧化时间为10min时,出现了鸟嘴效应。随着氧化时间增加,鸟嘴效应越加明显。说明氧化时间越长,氧化剂横向扩散越严重,鸟嘴效应越明显,鸟嘴越大。

图2 不同氧化时间时鸟嘴形貌 图3不同衬垫氧化层厚度时鸟嘴形貌

图3为不同衬垫氧化层厚度时鸟嘴形貌。由图可见,随着厚度增加,鸟嘴更长。说明衬垫氧化层厚度增加,会增强氧化剂横向扩散,并增强鸟嘴效应。

图4为不同氧化剂时鸟嘴形貌。由图可见,干氧氧化工艺鸟嘴效应远小于湿氧氧化。这主要是由于干氧氧化剂扩散速率远小于湿氧氧化剂,因此干氧氧化剂横向扩散速率也会远小于湿氧氧化剂,导致干氧氧化鸟嘴效应远小于湿氧氧化。

图4 不同氧化剂时鸟嘴形貌

(二)V型槽栅GaN高电子迁移率器件击穿特性仿真实验案例

A. 实验目的和意义

为了使学生能够更深入、直观地理解V型栅GaN高电子迁移率晶体管的研究意义,掌握V型栅对击穿电压的影响,这里采用一种成熟的器件与工艺TCAD仿真工具Silvaco来对V型栅GaN HEMT 器件的击穿特性进行模拟实验。

B. 实验步骤

(1)打开Silvaco软件中的deckbulid程序运行窗口,并编写模拟仿真程序。设置器件的基本结构。源漏间距5um,其中栅源间距1.5um,栅漏间距2.5um,栅长1um,AlGaN势垒层厚度为20nm,Si3N4厚度为80nm。

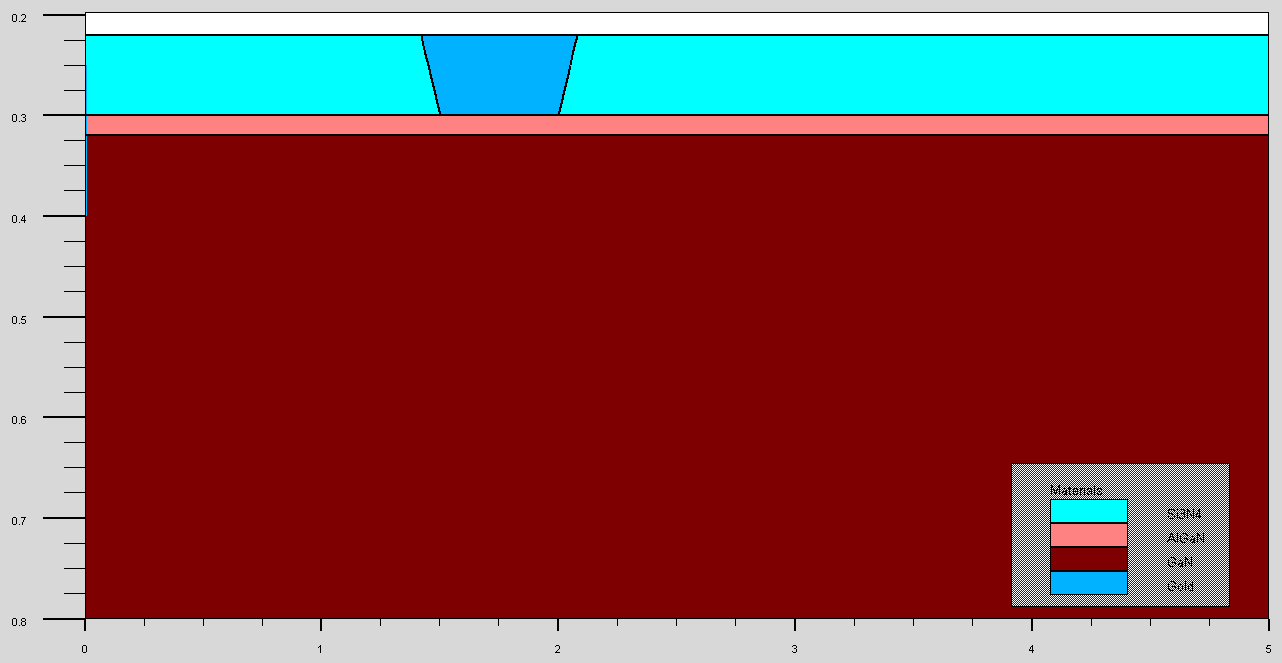

(2)设置材料的基本参数图5程序内容。用Tonyplot显示出器件的结构如图6所示,图内含有器件内部的各个信息,如掺杂浓度,场强大小等。选择plot—display---define—contours,在Quantity内选择Electric Field,点击OK,即可观察到图7。

图5 Silvaco软件运行界面 图6 V型栅器件结构仿真图

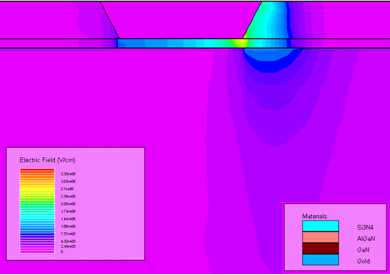

图7 为V型栅的电场强度分布图

(3)在Tonyplot窗口内,选择Tools—cultline,选择横向切割,在AlGaN势垒层内,从源处切割到漏处,即可出现新的窗口,单击鼠标右键,选择Electric Field,即可观察到器件内部的电场分布信息,如图8。

图8 不同栅结构器件内部的电场比较

(4)分析结果

C. 实验结果分析

图5为Silvaco软件中deckbulid程序运行窗口以及基本模拟程序。通过程序的编写,将所模拟设计的器件实际结构参数,采用虚拟的软件进行器件结构和特性的展示。

图6为Silvaco软件中V型栅GaN HEMT 器件结构展示图。从结构展示图中,将实际的器件结构采用虚拟仿真的模式展示到学生面前,帮助学生更生动的理解实际的器件结构。

图7为V型栅的电场强度分布图。我们可以看出,栅边缘处的电场强度很大,因此器件很容易在此处发生击穿。相对于普通栅,V型栅分散了栅处的电场密集度,降低了电场强度,因此能够提高器件的击穿电压,从而使得器件的功率特性能大幅度提高。

图8为从源端到漏端器件内部的电场强度值对比图。可以看到,栅边缘电场最大,V型栅电场值低于普通栅的电场值,因此击穿电压更大。

(三)Si基MOSFET器件强电磁脉冲辐照引起特性参数退化虚拟仿真案例

A. 实验目的和意义

强电磁脉冲是种破坏性极强的电磁干扰信号,高功率微波能导致电子设备中的半导体器件或集成电路特性退化、损伤甚至与烧毁,造成电子设备永久损坏。本实验通过搭建强电磁脉冲半导体器件虚拟平台,仿真nMOSFET器件在高功率微波(HPM)辐照下器件特性的退化的机理与物理过程。

B. 实验步骤

(1)登陆虚拟仿真实验平台,调用“Si基MOSFET器件强电磁脉冲辐照引起特性参数退化虚拟仿真”程序。

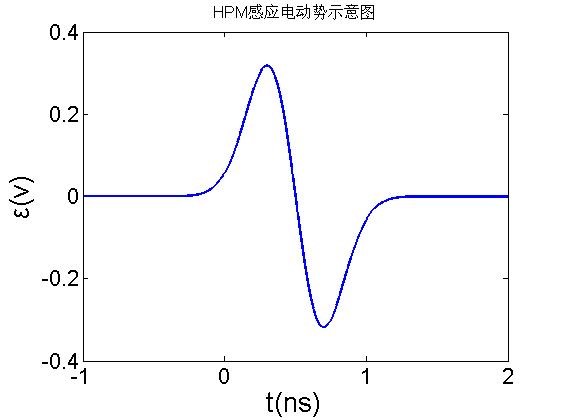

(2)栅极注入HPM的器件偏置,设置注入HPM参数,包括频率、脉宽以及功率,虚拟仿真栅极注入HPM感应电压波形;

(3)建立典型nMOSFET器件结构,定义结构参数(栅长,栅极厚度,漏源区掺杂浓度、结深等),虚拟仿真栅极注入HPM时,产生的热载流子注入到栅氧化层,引起界栅氧化面陷阱密度增加过程;

(4)仿真分析栅氧化面陷阱密度增加,引起的nMOSFET阈值电压、沟道电子迁移率变化;

(5)分析不同界面陷阱密度下器件的特性曲线,通过器件直流特性模型参数对比器件特性在HPM辐照下性能的退化。

C. 实验结果分析

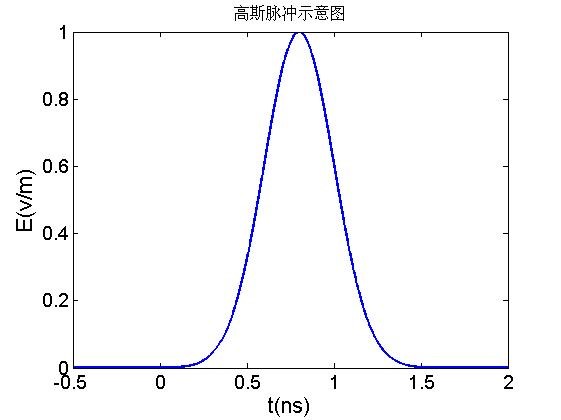

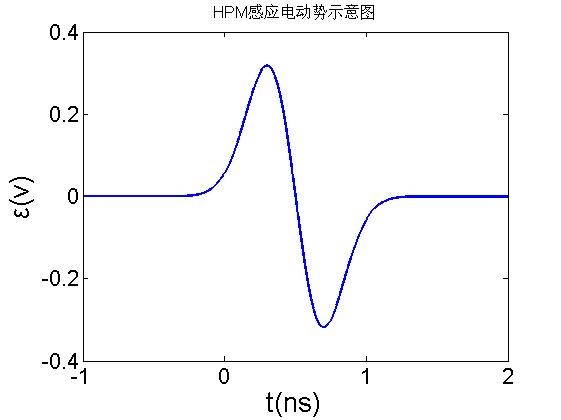

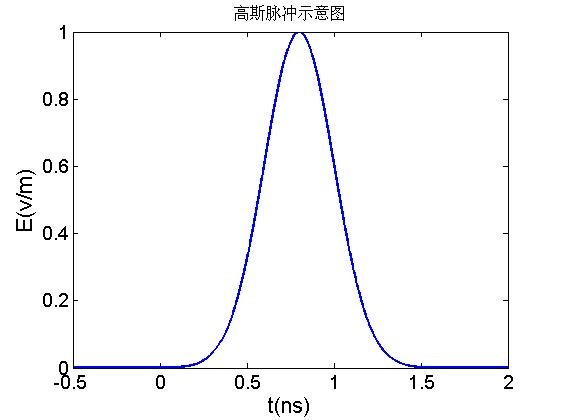

图9为HPM脉冲以及通过注入法感应电势波形。

(a) (b)

图9 (a)单个高斯脉冲的HPM示意图,(b)感应电动势示意图

图10为栅极注入HPM影响两种载流子结构图。

(a) (b)

图10 沟道热载流子(a)衬底热载流子,(b)示意图

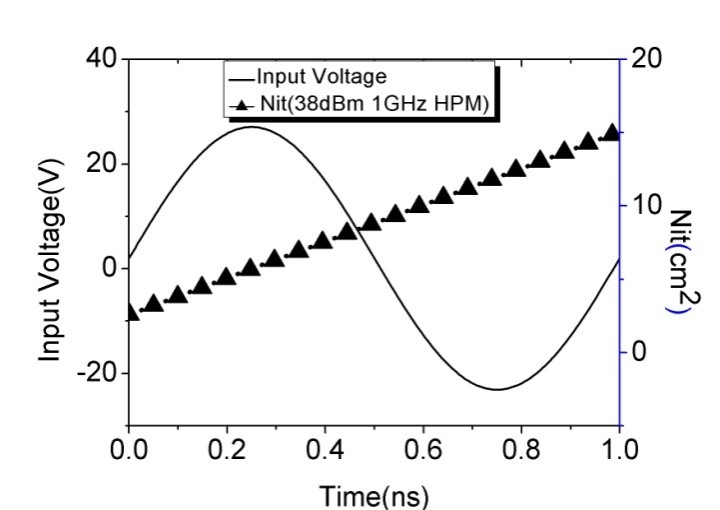

图11为栅氧化层界面陷阱密度随着HPM注入时间累计图。由图可见,随着HPM脉冲的持续作用下,界面陷阱逐渐增多。

图11 界面陷阱密度随HPM注入时间变化图

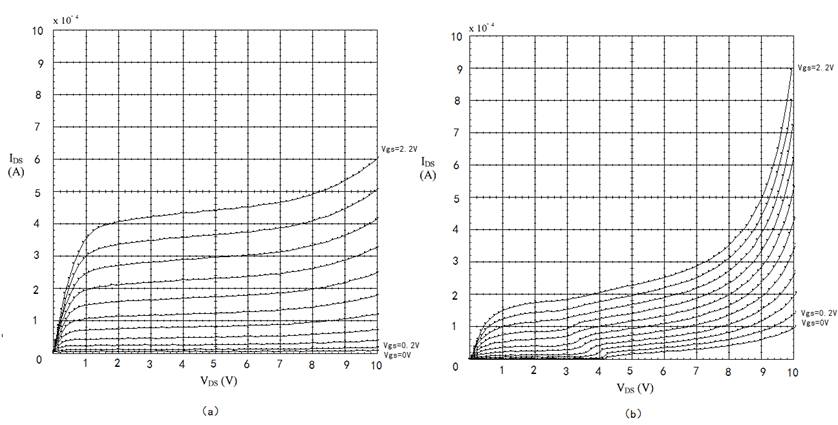

图12为虚拟测试HPM栅极注入前后器件直流输出特性曲线对比结果,显示HPM辐照下导致nMOSFET的阈值电压正向漂移、饱和漏电流下降、跨导降低,即器件电学特性参数出现退化

。

。

图12 nMOSFET虚拟测试的I-V特性曲线,辐照前(a),辐照后(b)

(四)Si基MOSFET器件强电磁脉冲辐照引起热电应力损伤虚拟仿真案例

A. 实验目的和意义

强电磁脉冲是种破坏性极强的电磁干扰信号,高功率微波能导致电子设备中的半导体器件或集成电路特性退化、损伤甚至与烧毁,造成电子设备永久损坏。本实验建立了高功率微波(HPM)在漏极感应电压以及器件二维热电响应虚拟平台,模拟器件在HPM作用下的响应,分析器件电场、温度分布,分析器件失效机理与过程。

B. 实验步骤

(1)登陆虚拟仿真实验平台,调用“Si基MOSFET器件强电磁脉冲辐照引起热电应力损伤虚拟仿真”程序。

(2)漏注入HPM的器件偏置,设置注入HPM参数,包括频率、脉宽以及功率,虚拟仿真栅极注入HPM感应电压波形;

(3)建立典型nMOSFET器件结构,定义结构参数(栅长,栅极厚度,漏源区掺杂浓度、结深等),虚拟仿真漏极注入HPM时,器件内部电场强度、电流密度;

(4)调整HPM注入时间,观测器件内部温度随着时间的变化情况;

(5)逐步增加HPM注入时间,直至器件内部温度超过直至硅熔点1688K,观测器件内部出现熔丝,观测器件特性变化。

C. 实验结果分析

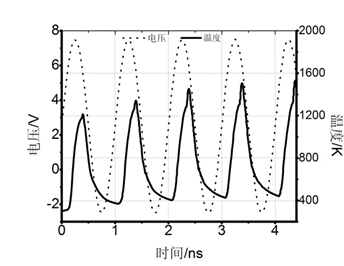

图13为HPM脉冲以及通过注入法感应电势波形。

(a) (b)

图13 (a)单个高斯脉冲的HPM示意图,(b)感应电动势示意图

图14显示,器件在HPM辐照下,电场和电流密度较大的区域以及最高内部高温区主要集中于漏区PN结处。

图15是微波信号作用下器件内部峰值温度随时间变化图,显示器件内部峰值温度总体趋势随着信号持续作用而不断上升,具有累积效应。

(a) (b) (c)

图14 器件内部电场强度(V/cm)(a);电子电流密度(A/)(b);温度分布(K)(c)

图15 界面陷阱密度随HPM注入时间变化图

从图16模拟结果分析可以看到,器件在HPM作用下的电效应和热效应相互影响使得器件温度持续上升,漏极附近靠近沟道区温度率先达到硅熔点(1688K),器件内部形成熔丝,随着HPM持续作用,熔丝的范围不断扩大,向沟道区扩展,导致器件损伤直至完全失效。

(a) (b)

图16 器件内部温度(a)与熔丝扩展(b)示意图

(五)4000/54/74系列电路仿真实验案例

A. 实验目的和意义

使学生能够更深入、更直观地理解集成电路逻辑中晶体管尺寸与电路性能之间的关系,掌握集成电路逻辑设计、电路优化方法,融汇所学数字集成电路、数字电子线路等理论知识。本实验采用行业通用设计流程与EDA仿真设计工具来完成指定性能指标的4000/54/74系列电路的设计仿真。

B. 实验步骤

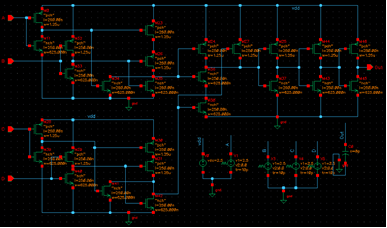

(1)分析目标电路的性能指标,完成电路的逻辑设计,并在指定工艺条件下,对完成电路器件尺寸及其驱动链级数和每一级器件尺寸的计算;

(2)运行cadence virtuso软件,打开composer窗口完成管级电路的设计输入,并标注每一个晶体管的尺寸;在电路输入端加入激励源;

(3)保存并检查电路正确性,选择analog环境,打开仿真窗口,设置运行目录,选择仿真的spice工具(Hspice/Spectra),指定仿真分析的工艺库模型以及当前分析的工艺角;

(4)选择要进行分析的种类(直流/交流/瞬态等),设置仿真条件;

(5)指定要观察的节点;

(6)运行仿真;

(7)在弹出的波形窗口观察分析仿真输出是否满足设计指标,如果不满足分析原因确定是否需要修改,然后修改优化设计;

C. 实验结果分析

(1)晶体管级电路输入与尺寸标注。

图17 4082芯片电路设计

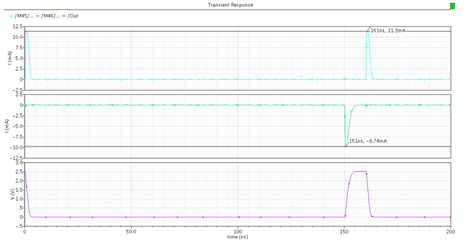

(2)晶体管参数计算仿真

题目要求:电源电压vdd=2.5v,电路速度为100MHZ以上,输出电流为8mA以上,负载8pf,上升、下降时间不大于最小周期的1/10。工艺条件 SMIC 0.25um的制造工艺,选择最小反相器的NMOS管L=0.25um,W=0.625um,PMOS管的L=0.25um,W=1.25um,进行电路尺寸计算。

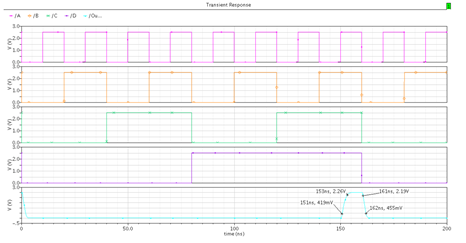

对图17电路进行Hspice瞬态仿真,结果如图18,19所示,由图18可以看到,在信号由0到1时,其输出泄漏电流达到9mA,在信号由1到0时,其输出灌电流达到11mA,满足设计指标(不小于8mA);由图19可见输出信号上升时间2ns,下降时间1ns,脉冲宽度10ns,满足时序指标要求。

图18输出端电流波形

图19逻辑功能与输出时序仿真图